- жөҸи§Ҳ: 1477473 ж¬Ў

-

ж–Үз« еҲҶзұ»

зӨҫеҢәзүҲеқ—

- жҲ‘зҡ„иө„и®Ҝ ( 0)

- жҲ‘зҡ„и®әеқӣ ( 0)

- жҲ‘зҡ„й—®зӯ” ( 0)

еӯҳжЎЈеҲҶзұ»

- 2014-11 ( 6)

- 2014-10 ( 2)

- 2014-09 ( 2)

- жӣҙеӨҡеӯҳжЎЈ...

жңҖж–°иҜ„и®ә

-

alcoholпјҡ

Androidзҡ„зүҲжң¬и¶ҠдҪҺпјҢе°ұи¶ҠжҳҺжҳҫ

Android дёӢжӢүеҲ·ж–°жҺ§д»¶д№ӢScrollViewзүҲжң¬е®һзҺ° -

alcoholпјҡ

жҘјдё»пјҢиҝҷжңүдёӘbugе‘ҖпјҢе°ұжҳҜеңЁдёӢжӢүеҲ°дёҖе®ҡдҪҚзҪ®ж—¶пјҢtopдјҡиҰҶзӣ–еҶ…е®№ ...

Android дёӢжӢүеҲ·ж–°жҺ§д»¶д№ӢScrollViewзүҲжң¬е®һзҺ° -

atomduanпјҡ

http://www.grobmeier.de/the-10- ...

зҰ…йҒ“зЁӢеәҸе‘ҳзҡ„10жқЎеҺҹеҲҷ -

jobboleпјҡ

жңӢеҸӢпјҢиҪ¬иҪҪж–Үз« пјҢж•…ж„ҸдёҚдҝқз•ҷеҲ йҷӨзҪІеҗҚйӮЈдёҖиЎҢпјҢжҳҜдёҚжҳҜдёҚйҒ“еҫ·пјҹеҺҹж–ҮеҮә ...

зҰ…йҒ“зЁӢеәҸе‘ҳзҡ„10жқЎеҺҹеҲҷ -

jiuyueheпјҡ

ж„ҹи§үиҝҷе°ұжҳҜеңЁиҜҙжҲ‘е•Ҡ

зҰ…йҒ“зЁӢеәҸе‘ҳзҡ„10жқЎеҺҹеҲҷ

u-bootеҲҶжһҗпјҲдёҖпјү

дёҖгҖҒbootloaderзҡ„жҰӮеҝө

з®ҖеҚ•зҡ„иҜҙпјҢbootloaderе°ұжҳҜеңЁж“ҚдҪңзі»з»ҹиҝҗиЎҢд№ӢеүҚиҝҗиЎҢзҡ„дёҖж®өе°ҸзЁӢеәҸпјҢйҖҡиҝҮиҝҷж®өе°ҸзЁӢеәҸпјҢжҲ‘们еҸҜд»ҘеҲқе§ӢеҢ–硬件и®ҫеӨҮпјҢз®ҖеҺҶеҶ…еӯҳз©әй—ҙжҳ е°„еӣҫпјҢд»ҺиҖҢе°Ҷзі»з»ҹзҡ„иҪҜ硬件зҺҜеўғеёҰеҲ°дёҖдёӘеҗҲйҖӮзҡ„зҡ„зҠ¶жҖҒпјҢдёҖиҫ№жңҖз»Ҳи°ғз”Ёж“ҚдҪңзі»з»ҹеҶ…ж ёеҮҶеӨҮеҘҪжӯЈзЎ®зҡ„зҺҜеўғгҖӮ

йҖҡеёёпјҢbootloaderжҳҜдёҘйҮҚзҡ„дҫқиө–дәҺ硬件иҖҢе®һзҺ°зҡ„пјҢзү№еҲ«еңЁеөҢе…ҘејҸдё–з•ҢпјҢе»әз«ӢдёҖдёӘйҖҡз”Ёзҡ„bootloaderеҮ д№ҺжҳҜдёҚеҸҜиғҪзҡ„пјҢе°Ҫз®ЎеҰӮжӯӨпјҢжҲ‘们д»Қ然еҸҜд»ҘеҜ№bootloaderеҪ’зәіеҮәдёҖдәӣйҖҡз”Ёзҡ„жҰӮеҝөжқҘпјҢд»ҘжҢҮеҜјз”ЁжҲ·зү№е®ҡзҡ„bootloaderи®ҫи®ЎдёҺе®һзҺ°гҖӮ

еҪ“然пјҢеңЁarm7дёҺarm9зҡ„ејҖеҸ‘еә”з”ЁдёӯпјҢд№ҹжңүи®ёеӨҡжҳҜдёҚйңҖиҰҒlinuxж“ҚдҪңзі»з»ҹзҡ„пјҢиҖҢжҳҜзӣҙжҺҘејҖеҸ‘иЈёжңәзҡ„д»Јз ҒпјҢеҲ«д»Ҙдёәе°ұдёҚиҰҒbootloaderдәҶпјҢеҸҚиҖҢеҸҜд»ҘеҲ©з”ЁbootloaderеҠ еҝ«иЈёжңәзҡ„ејҖеҸ‘пјҢеә”з”ЁеңЁbootloaderиҝҗиЎҢеҗҺпјҢжҜ”еҰӮu-bootпјҢеҹәжң¬дёҠж”ҜжҢҒжүҖжңүзҡ„еӨ–и®ҫпјҢеҸҜд»ҘиҜҙubootе°ұжҳҜдёҖдёӘе°ҸеһӢзҡ„ж“ҚдҪңзі»з»ҹпјҢиЈёжңәд»Јз ҒеҸҜд»ҘзӣҙжҺҘе»әз«ӢеңЁubootд№ӢдёҠпјҢжңүе…ҙи¶ЈеҸҜд»ҘеҒҡдёҖдәӣиҝҷж ·зҡ„ејҖеҸ‘гҖӮдёҚеңЁжң¬ж–Үзҡ„и®Ёи®әиҢғеӣҙгҖӮ

дәҢгҖҒbootloaderзҡ„еҲҶеұӮ

йҖҡеёёеӨҡйҳ¶ж®өзҡ„ Boot Loader иғҪжҸҗдҫӣжӣҙдёәеӨҚжқӮзҡ„еҠҹиғҪпјҢд»ҘеҸҠжӣҙеҘҪзҡ„еҸҜ移жӨҚжҖ§гҖӮд»ҺеӣәжҖҒеӯҳеӮЁи®ҫеӨҮдёҠеҗҜеҠЁзҡ„ Boot Loader еӨ§еӨҡйғҪжҳҜ 2 йҳ¶ж®өзҡ„еҗҜеҠЁиҝҮзЁӢпјҢд№ҹеҚіеҗҜеҠЁиҝҮзЁӢеҸҜд»ҘеҲҶдёә stage 1 е’Ң stage 2 дёӨйғЁеҲҶгҖӮз”ұдәҺ Boot Loader зҡ„е®һзҺ°дҫқиө–дәҺ CPU зҡ„дҪ“зі»з»“жһ„пјҢеӣ жӯӨеӨ§еӨҡж•° Boot Loader йғҪеҲҶдёә stage1 е’Ң stage2 дёӨеӨ§йғЁеҲҶгҖӮдҫқиө–дәҺ CPU дҪ“зі»з»“жһ„зҡ„д»Јз ҒпјҢжҜ”еҰӮи®ҫеӨҮеҲқе§ӢеҢ–д»Јз ҒзӯүпјҢйҖҡеёёйғҪж”ҫеңЁ stage1 дёӯпјҢиҖҢдё”йҖҡеёёйғҪз”ЁжұҮзј–иҜӯиЁҖжқҘе®һзҺ°пјҢд»ҘиҫҫеҲ°зҹӯе°ҸзІҫжӮҚзҡ„зӣ®зҡ„гҖӮиҖҢ stage2 еҲҷйҖҡеёёз”ЁCиҜӯиЁҖжқҘе®һзҺ°пјҢиҝҷж ·еҸҜд»Ҙе®һзҺ°з»ҷеӨҚжқӮзҡ„еҠҹиғҪпјҢиҖҢдё”д»Јз Ғдјҡе…·жңүжӣҙеҘҪзҡ„еҸҜиҜ»жҖ§е’ҢеҸҜ移жӨҚжҖ§гҖӮзҶҹзҹҘзҡ„ubootе°ұжҳҜеҲҶдёәstage1дёҺstage2.

дёүгҖҒbootloaderзҡ„дё»иҰҒд»»еҠЎдёҺе…ёеһӢз»“жһ„жЎҶжһ¶

Boot Loader зҡ„ stage1 йҖҡеёёеҢ…жӢ¬д»ҘдёӢжӯҘйӘӨ(д»Ҙжү§иЎҢзҡ„е…ҲеҗҺйЎәеәҸ)пјҡ

-

硬件и®ҫеӨҮеҲқе§ӢеҢ–гҖӮ

-

дёәеҠ иҪҪ Boot Loader зҡ„ stage2 еҮҶеӨҮ RAM з©әй—ҙгҖӮ

-

жӢ·иҙқ Boot Loader зҡ„ stage2 еҲ° RAM з©әй—ҙдёӯгҖӮ

-

и®ҫзҪ®еҘҪе Ҷж ҲгҖӮ

-

и·іиҪ¬еҲ° stage2 зҡ„ C е…ҘеҸЈзӮ№гҖӮ

Boot Loader зҡ„ stage2 йҖҡеёёеҢ…жӢ¬д»ҘдёӢжӯҘйӘӨ(д»Ҙжү§иЎҢзҡ„е…ҲеҗҺйЎәеәҸ)пјҡ

-

еҲқе§ӢеҢ–жң¬йҳ¶ж®өиҰҒдҪҝз”ЁеҲ°зҡ„硬件и®ҫеӨҮгҖӮ

-

жЈҖжөӢзі»з»ҹеҶ…еӯҳжҳ е°„(memory map)гҖӮ

-

е°Ҷ kernel жҳ еғҸе’Ңж №ж–Ү件系з»ҹжҳ еғҸд»Һ flash дёҠиҜ»еҲ° RAM з©әй—ҙдёӯгҖӮ

-

дёәеҶ…ж ёи®ҫзҪ®еҗҜеҠЁеҸӮж•°гҖӮ

- и°ғз”ЁеҶ…ж ёгҖӮ

(1)еҹәжң¬зҡ„硬件еҲқе§ӢеҢ–

иҝҷжҳҜ Boot Loader дёҖејҖе§Ӣе°ұжү§иЎҢзҡ„ж“ҚдҪңпјҢе…¶зӣ®зҡ„жҳҜдёә stage2 зҡ„жү§иЎҢд»ҘеҸҠйҡҸеҗҺзҡ„ kernel зҡ„жү§иЎҢеҮҶеӨҮеҘҪдёҖдәӣеҹәжң¬зҡ„硬件зҺҜеўғгҖӮе®ғйҖҡеёёеҢ…жӢ¬д»ҘдёӢжӯҘйӘӨпјҲд»Ҙжү§иЎҢзҡ„е…ҲеҗҺйЎәеәҸпјүпјҡ

1пјҺеұҸи”ҪжүҖжңүзҡ„дёӯж–ӯгҖӮдёәдёӯж–ӯжҸҗдҫӣжңҚеҠЎйҖҡеёёжҳҜ OS и®ҫеӨҮй©ұеҠЁзЁӢеәҸзҡ„иҙЈд»»пјҢеӣ жӯӨеңЁ Boot Loader зҡ„жү§иЎҢе…ЁиҝҮзЁӢдёӯеҸҜд»ҘдёҚеҝ…е“Қеә”д»»дҪ•дёӯж–ӯгҖӮдёӯж–ӯеұҸи”ҪеҸҜд»ҘйҖҡиҝҮеҶҷ CPU зҡ„дёӯж–ӯеұҸи”ҪеҜ„еӯҳеҷЁжҲ–зҠ¶жҖҒеҜ„еӯҳеҷЁпјҲжҜ”еҰӮ ARM зҡ„ CPSR еҜ„еӯҳеҷЁпјүжқҘе®ҢжҲҗгҖӮ

2пјҺи®ҫзҪ® CPU зҡ„йҖҹеәҰе’Ңж—¶й’ҹйў‘зҺҮгҖӮ

3пјҺRAM еҲқе§ӢеҢ–гҖӮеҢ…жӢ¬жӯЈзЎ®ең°и®ҫзҪ®зі»з»ҹзҡ„еҶ…еӯҳжҺ§еҲ¶еҷЁзҡ„еҠҹиғҪеҜ„еӯҳеҷЁд»ҘеҸҠеҗ„еҶ…еӯҳеә“жҺ§еҲ¶еҜ„еӯҳеҷЁзӯүгҖӮ

4пјҺеҲқе§ӢеҢ– LEDгҖӮе…ёеһӢең°пјҢйҖҡиҝҮ GPIO жқҘй©ұеҠЁ LEDпјҢе…¶зӣ®зҡ„жҳҜиЎЁжҳҺзі»з»ҹзҡ„зҠ¶жҖҒжҳҜ OK иҝҳжҳҜ ErrorгҖӮеҰӮжһңжқҝеӯҗдёҠжІЎжңү LEDпјҢйӮЈд№Ҳд№ҹеҸҜд»ҘйҖҡиҝҮеҲқе§ӢеҢ– UART еҗ‘дёІеҸЈжү“еҚ° Boot Loader зҡ„ Logo еӯ—з¬ҰдҝЎжҒҜжқҘе®ҢжҲҗиҝҷдёҖзӮ№гҖӮ

5пјҺе…ій—ӯ CPU еҶ…йғЁжҢҮд»ӨпјҸж•°жҚ® cacheгҖӮ(2)дёәеҠ иҪҪ stage2 еҮҶеӨҮ RAM з©әй—ҙ

дёәдәҶиҺ·еҫ—жӣҙеҝ«зҡ„жү§иЎҢйҖҹеәҰпјҢйҖҡеёёжҠҠ

stage2 еҠ иҪҪеҲ° RAM з©әй—ҙдёӯжқҘжү§иЎҢпјҢеӣ жӯӨеҝ…йЎ»дёәеҠ иҪҪ Boot Loader зҡ„ stage2 еҮҶеӨҮеҘҪдёҖж®өеҸҜз”Ёзҡ„ RAM з©әй—ҙиҢғеӣҙгҖӮ

(3) жӢ·иҙқ stage2 еҲ° RAM дёӯ

жӢ·иҙқж—¶иҰҒзЎ®е®ҡдёӨзӮ№пјҡ(1) stage2 зҡ„еҸҜжү§иЎҢжҳ иұЎеңЁеӣәжҖҒеӯҳеӮЁи®ҫеӨҮзҡ„еӯҳж”ҫиө·е§Ӣең°еқҖе’Ңз»Ҳжӯўең°еқҖпјӣ(2) RAM з©әй—ҙзҡ„иө·е§Ӣең°еқҖгҖӮ

(4)и®ҫзҪ®е Ҷж ҲжҢҮй’Ҳ sp

е Ҷж ҲжҢҮй’Ҳзҡ„и®ҫзҪ®жҳҜдёәдәҶжү§иЎҢ C иҜӯиЁҖд»Јз ҒдҪңеҘҪеҮҶеӨҮгҖӮйҖҡеёёжҲ‘们еҸҜд»ҘжҠҠ sp зҡ„еҖји®ҫзҪ®дёә(stage2_end-4)пјҢд№ҹеҚіеңЁ 3.1.2 иҠӮжүҖе®үжҺ’зҡ„йӮЈдёӘ 1MB зҡ„ RAM з©әй—ҙзҡ„жңҖйЎ¶з«Ҝ(е Ҷж Ҳеҗ‘дёӢз”ҹй•ҝ)гҖӮ

жӯӨеӨ–пјҢеңЁи®ҫзҪ®е Ҷж ҲжҢҮй’Ҳ sp д№ӢеүҚпјҢд№ҹеҸҜд»Ҙе…ій—ӯ led зҒҜпјҢд»ҘжҸҗзӨәз”ЁжҲ·жҲ‘们еҮҶеӨҮи·іиҪ¬еҲ° stage2гҖӮ

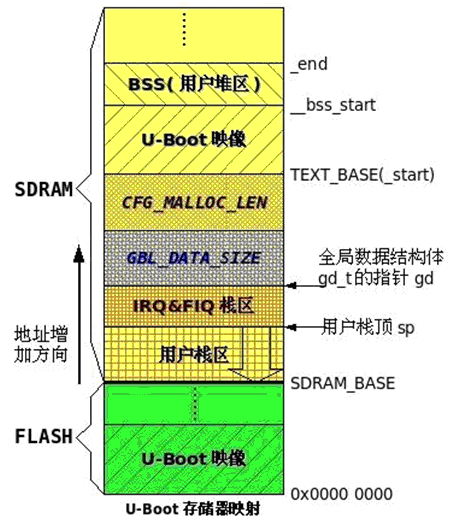

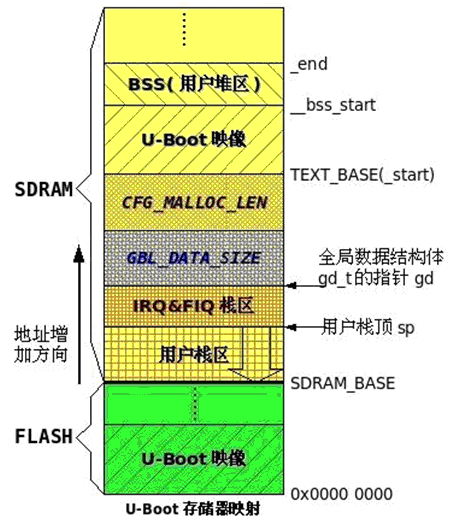

з»ҸиҝҮдёҠиҝ°иҝҷдәӣжү§иЎҢжӯҘйӘӨеҗҺпјҢзі»з»ҹзҡ„зү©зҗҶеҶ…еӯҳеёғеұҖеә”иҜҘеҰӮдёӢеӣҫ2жүҖзӨәгҖӮ

(5) и·іиҪ¬еҲ° stage2 зҡ„ C е…ҘеҸЈзӮ№

еңЁдёҠиҝ°дёҖеҲҮйғҪе°ұз»ӘеҗҺпјҢе°ұеҸҜд»Ҙи·іиҪ¬еҲ° Boot Loader зҡ„ stage2 еҺ»жү§иЎҢдәҶгҖӮжҜ”еҰӮпјҢеңЁ ARM зі»з»ҹдёӯпјҢиҝҷеҸҜд»ҘйҖҡиҝҮдҝ®ж”№ PC еҜ„еӯҳеҷЁдёәеҗҲйҖӮзҡ„ең°еқҖжқҘе®һзҺ°гҖӮ

дә”гҖҒstage2

1еҲқе§ӢеҢ–жң¬йҳ¶ж®өиҰҒдҪҝз”ЁеҲ°зҡ„硬件и®ҫеӨҮ

2 жЈҖжөӢзі»з»ҹзҡ„еҶ…еӯҳжҳ е°„пјҲmemory mapпјү3

еҠ иҪҪеҶ…ж ёжҳ еғҸе’Ңж №ж–Ү件系з»ҹжҳ еғҸ

4

и®ҫзҪ®еҶ…ж ёзҡ„еҗҜеҠЁеҸӮж•°

5

и°ғз”ЁеҶ…ж ё

е…ӯгҖҒеҲ°иҝҷйҮҢпјҢbootloaderзҡ„е·ҘдҪңе°ұе®ҢжҲҗдәҶпјҢејҖе§Ӣжңүlinux kernelз®ЎзҗҶ硬件гҖӮ

**********************************************************************************

дёӢйқўејҖе§ӢеҲҶжһҗu-bootпјҢе…ҲзңӢдёҖдёӢu-bootзҡ„еӯҳеӮЁеҷЁжҳ е°„еӣҫ

ubootдёҠз”өиҝҗиЎҢзҡ„第дёҖдёӘж–Ү件жҳҜstart.sпјҢе®ғдҪҚдәҺжҜҸдёӘж–Ү件еӨ№cpuдёӢзҡ„дёҚеҗҢе№іеҸ°дёӯпјҢжҜ”еҰӮmini2440зҡ„start.sдҪҚдәҺarm920tдёӢ

#include <common.h>

#include <config.h>

/*

*************************************************************************

*

* Jump vector table as in table 3.1 in [1]

*

*************************************************************************

*/

.globl _start

_start: b

start_code ;дёҠз”өиҝҗиЎҢзҡ„第дёҖжқЎжҢҮд»ӨпјҢи·іиҪ¬еҲ°start_codeеӨ„жү§иЎҢ

ldr pc, _undefined_instruction;жӯӨеӨ„ејӮеёёеӨ„зҗҶзҡ„йЎәеәҸжҳҜеӣәе®ҡзҡ„

ldr pc, _software_interrupt

ldr pc, _prefetch_abort

ldr pc, _data_abort

ldr pc, _not_used

ldr pc, _irq

ldr pc, _fiq

_undefined_instruction: .word undefined_instruction

_software_interrupt: .word software_interrupt

_prefetch_abort: .word prefetch_abort

_data_abort: .word data_abort

_not_used: .word not_used

_irq: .word irq

_fiq: .word fiq

.balignl 16,0xdeadbeef

/*

*************************************************************************

*

* Startup Code (called from the ARM reset exception vector)

*

* do important init only if we don't start from memory!

* relocate armboot to ram

* setup stack

* jump to second stage

*

*************************************************************************

*/

/*еӯҳеӮЁеҷЁжҳ е°„пјҢеҰӮдёҠеӣҫ*/

_TEXT_BASE:

.word TEXT_BASE

.globl _armboot_start

_armboot_start:

.word _start

/*

* These are defined in the board-specific linker script.

*/

.globl _bss_start

_bss_start:

.word __bss_start

.globl _bss_end

_bss_end:

.word _end

#ifdef CONFIG_USE_IRQ

/* IRQ stack memory (calculated at run-time) */

.globl IRQ_STACK_START

IRQ_STACK_START:

.word 0x0badc0de

/* IRQ stack memory (calculated at run-time) */

.globl FIQ_STACK_START

FIQ_STACK_START:

.word 0x0badc0de

#endif

/*

* the actual start code

зңҹжӯЈзҡ„жҢҮд»ӨејҖе§ӢеӨ„

*/

start_code:

/*

* set the cpu to SVC32 mode

*/

mrs r0, cpsr

bic r0, r0, #0x1f;иҝҷйҮҢиҰҒеҜ№з…§2440зҡ„datasheetдёӯзҡ„cpsrеҜ„еӯҳеҷЁпјҢеұҸи”ҪйҷӨдәҶmodeзҡ„жүҖжңүдҪҚ

orr r0, r0, #0xd3;и®ҫзҪ®modeдёәsvcпјҲи¶…зә§з”ЁжҲ·пјҢжңҖй«ҳжқғйҷҗпјүпјҢжӯӨеӨ„irqпјҢfiqзҪ®1пјҢе…ій—ӯдёӯж–ӯ

msr cpsr, r0

@ bl coloured_LED_init;еҸҜд»ҘзӮ№дә®дёҖдёӘledпјҢжҢҮзӨәu-bootе·Із»ҸејҖе§ӢиҝҗиЎҢпјҢеҮҪж•°еңЁboardж–Ү件еӨ№дёӢзҡ„е…·дҪ“жқҝзә§ж–Ү件йҮҢ

@ bl red_LED_on;жҢҮд»ӨblжҳҜеёҰиҝ”еӣһзҡ„и·іиҪ¬пјҢиҝҗиЎҢе®Ңred_LED_onеҮҪж•°еҗҺпјҢдјҡеӣһеҲ°жӯӨеӨ„继з»ӯеҫҖдёӢжү§иЎҢ

#if defined(CONFIG_AT91RM9200DK) || defined(CONFIG_AT91RM9200EK)

/*

* relocate exception table

*/

ldr r0, =_start

ldr r1, =0x0

mov r2, #16

copyex:

subs r2, r2, #1

ldr r3, [r0], #4

str r3, [r1], #4

bne copyex

#endif

#ifdef CONFIG_S3C24X0

/* turn off the watchdog */

/*s3c2440жүӢеҶҢдёӯжңүд»ҘдёӢзү№ж®ҠеҜ„еӯҳеҷЁзҡ„еҶ…еӯҳең°еқҖ*/

# if defined(CONFIG_S3C2400)

# define pWTCON 0x15300000

# define INTMSK 0x14400008/* Interupt-Controller base addresses */

# define CLKDIVN 0x14800014/* clock divisor register */

#else

# define pWTCON 0x53000000

# define INTMSK 0x4A000008/* Interupt-Controller base addresses */

# define INTSUBMSK 0x4A00001C

# define CLKDIVN 0x4C000014/* clock divisor register */

# endif

#define CLK_CTL_BASE 0x4C000000/* tekkaman */

#define MDIV_405 0x7f << 12/* tekkaman */

#define PSDIV_405 0x21/* tekkaman */

#define MDIV_200 0xa1 << 12/* tekkaman */

#define PSDIV_200 0x31/* tekkaman */

ldr r0, =pWTCON;еҠ иҪҪең°еқҖ0x53000000еҲ°r0

mov r1, #0x0;и®ҫзҪ®r1дёә0x0

str r1, [r0];еңЁең°еқҖ0x53000000еӨ„еҶҷ0пјҢе…ій—ӯwatchdog

/*

* mask all IRQs by setting all bits in the INTMR - default

*/

mov r1, #0xffffffff

ldr r0, =INTMSK

str r1, [r0];INTMSKдёӯж–ӯеұҸи”ҪеҜ„еӯҳеҷЁпјҢ32дҪҚеҜ„еӯҳеҷЁпјҢжҜҸдёҖдёӘйғҪжҳҜе’ҢдёҖдёӘдёӯж–ӯжәҗзӣёе…іпјҢзҪ®1еҲҷдёҚе“Қеә”дёӯж–ӯиҜ·жұӮпјҢиҝҷйҮҢдёҚе“Қеә”жүҖжңүиҜ·жұӮпјҢе…ій—ӯдёӯж–ӯпјҢй…ҚеҗҲcpsrзҡ„fдёҺiдҪҚ

# if defined(CONFIG_S3C2410)

ldr r1, =0x7ff

ldr r0, =INTSUBMSK

str r1, [r0]

# endif

#if defined(CONFIG_S3C2440)

ldr r1, =0x7fff

ldr r0, =INTSUBMSK;INTSUBMSKеӯҗдёӯж–ӯеұҸи”ҪеҜ„еӯҳеҷЁпјҢдёә15дҪҚпјҢзҪ®1дёҚе“Қеә”дёӯж–ӯиҜ·жұӮпјҢеҗҢINTMSK

str r1, [r0]

#endif

/*и®ҫзҪ®ж—¶й’ҹйў‘зҺҮ

*s3c2440жңүдёүдёӘж—¶й’ҹпјҢFCLKпјҢHCLKпјҢPCLK

*FCLK is used by ARM920TпјҢеҶ…ж ёж—¶й’ҹпјҢдё»йў‘

*HCLK is used for AHB bus ,which is used by the ARM920T, the memory controller,the interrupt controller,the lcd controller,the dma,and*usb host blockжҳҜжҖ»зәҝж—¶й’ҹпјҢеҢ…жӢ¬дё»иҰҒжҺ§еҲ¶еҷЁ

*PCLK is used for APB bus, which is used by the peripherals such as wdt,iis,i2c,pwm timer,mmc interface,adc,uart,gpio,rtc and spiеҚіжҺҘеҸЈж—¶й’ҹпјҢ

*дёүдёӘж—¶й’ҹйҖҡеёёи®ҫдёә1:4:8жҲ–иҖ…1:3:6

*/

#if defined(CONFIG_S3C2440)

/* FCLK:HCLK:PCLK = 1:4:8 */

ldr r0, =CLKDIVN;

mov r1, #5

str r1, [r0]

/*CP15зі»з»ҹжҺ§еҲ¶еҚҸеӨ„зҗҶеҷЁпјҢйҖҡиҝҮеҚҸеӨ„зҗҶеҷЁжҢҮд»Өmrcе’ҢmcrжҸҗдҫӣе…·дҪ“зҡ„еҜ„еӯҳеҷЁжқҘй…ҚзҪ®е’ҢжҺ§еҲ¶cachesпјҢmmuпјҢдҝқжҠӨзі»з»ҹпјҢй…ҚзҪ®ж—¶й’ҹжЁЎејҸпјҲеңЁbootloaderж—¶й’ҹеҲқе§ӢеҢ–ж—¶з”ЁеҲ°пјүпјҢе…·дҪ“еҸӮзңӢarm architecture reference manual 2nd 第487йЎө*/

mrcp15, 0, r1, c1, c0, 0

orr r1, r1, #0xc0000000

mcr p15, 0, r1, c1, c0, 0

/*CLK_CTL_BASE=

0x4c000000

*MPLLCON=0x4c000004

*MDIV_405=0x7f<<12пјҢйҖүжӢ©12MHzиҫ“е…Ҙйў‘зҺҮпјҢ405MMzиҫ“еҮәйў‘зҺҮ

*MPLLCONз”ұMDIV[19:12] \ PDIV[9:4] \ SDIV[1:0]еҶіе®ҡ

*еҜ№з…§datasheetпјҢmdivдёә0x7fпјҢpdivдёә0x02пјҢsdivдёә0x01

*/

mov r1, #CLK_CTL_BASE

mov r2, #MDIV_405

add r2, r2, #PSDIV_405

str r2, [r1, #0x04]/* MPLLCON tekkaman */

#else

/* FCLK:HCLK:PCLK = 1:2:4 */

/* default FCLK is 120 MHz ! */

ldr r0, =CLKDIVN

mov r1, #3

str r1, [r0]

mrc p15, 0, r1, c1, c0, 0

orr r1, r1, #0xc0000000

mcr p15, 0, r1, c1, c0, 0/*write ctrl register tekkaman*/

mov r1, #CLK_CTL_BASE/* tekkaman*/

mov r2, #MDIV_200

add r2, r2, #PSDIV_200

str r2, [r1, #0x04]

#endif

#endif /* CONFIG_S3C24X0 */

/*

* we do sys-critical inits only at reboot,

* not when booting from ram!

*/

#ifndef CONFIG_SKIP_LOWLEVEL_INIT ;еҰӮжһңжІЎжңүе®ҡд№үCONFIG_SKIP_LOWLEVEL_INITпјҢе°ұи·іиҪ¬еҲ°cpu_init_critеӨ„иҝӣиЎҢеҲқе§ӢеҢ–е·ҘдҪңпјҢжҲ‘们еҪ“然дёҚдјҡи°ғиҝҮеә•еұӮзҡ„еҲқе§ӢеҢ–пјҢеӣ дёәLOWLEVEL_INITдјҡеҜ№жҲ‘们зҡ„sdramиҝӣиЎҢеҲқе§ӢеҢ–пјҢиҝҷеҜ№жҲ‘们зҡ„cpuжҳҜеҝ…иҰҒзҡ„

bl cpu_init_crit;еҮҪж•°дҪҚзҪ®пјҹ

#endif

/***************** CHECK_CODE_POSITION *****************************************

*жЈҖжҹҘд»Јз ҒиҝҗиЎҢзҡ„дҪҚзҪ®пјҢеӣ дёә_startжҳҜзЁӢеәҸжү§иЎҢзҡ„第дёҖжқЎд»Јз ҒпјҢжүҖд»ҘеҰӮжһңеңЁflashдёӯиҝҗиЎҢпјҢ_startзҡ„еҖјеә”дёә0пјҢ

*иҖҢеҰӮжһңеңЁramдёӯиҝҗиЎҢпјҢ_startеҲҷдёҚдёә0пјҢдҪҶжҳҜ_startдёәдҪ•зӯүдәҺ_TEXT_BASEпјҹ

*/

adr r0, _start/* r0 <- current position of code */

ldr r1, _TEXT_BASE/* test if we run from flash or RAM */

cmp r0, r1/* don't reloc during debug */

beq stack_setup;иӢҘr0==r1пјҢеҲҷи·іиҪ¬еҲ°stack_setup

/***************** CHECK_CODE_POSITION ******************************************/

/***************** CHECK_BOOT_FLASH ******************************************/

ldr r1, =( (4<<28)|(3<<4)|(3<<2) )/* address of Internal SRAM 0x4000003C*/

mov r0, #0/* r0 = 0 */

str r0, [r1]

mov r1, #0x3c/* address of men 0x0000003C*/

ldr r0, [r1]

cmp r0, #0

bne relocate

/* recovery */

ldr r0, =(0xdeadbeef)

ldr r1, =( (4<<28)|(3<<4)|(3<<2) )

str r0, [r1]

/***************** CHECK_BOOT_FLASH ******************************************/

/***************** NAND_BOOT *************************************************/

#define LENGTH_UBOOT 0x60000

#define NAND_CTL_BASE 0x4E000000

#ifdef CONFIG_S3C2440

/* Offset */

#define oNFCONF 0x00

#define oNFCONT 0x04

#define oNFCMD 0x08

#define oNFSTAT 0x20

@ reset NAND

mov r1, #NAND_CTL_BASE

ldr r2, =( (7<<12)|(7<<8)|(7<<4)|(0<<0) )

str r2, [r1, #oNFCONF]

ldr r2, [r1, #oNFCONF]

ldr r2, =( (1<<4)|(0<<1)|(1<<0) )@ Active low CE Control

str r2, [r1, #oNFCONT]

ldr r2, [r1, #oNFCONT]

ldr r2, =(0x6)@ RnB Clear

str r2, [r1, #oNFSTAT]

ldr r2, [r1, #oNFSTAT]

mov r2, #0xff@ RESET command

strb r2, [r1, #oNFCMD]

mov r3, #0@ wait

nand1:

add r3, r3, #0x1

cmp r3, #0xa

blt nand1

nand2:

ldr r2, [r1, #oNFSTAT]@ wait ready

tst r2, #0x4

beq nand2

ldr r2, [r1, #oNFCONT]

orr r2, r2, #0x2@ Flash Memory Chip Disable

str r2, [r1, #oNFCONT]

@ get read to call C functions (for nand_read())

ldr sp, DW_STACK_START@ setup stack pointer

mov fp, #0@ no previous frame, so fp=0

@ copy U-Boot to RAM

ldr r0, =TEXT_BASE

mov r1, #0x0

mov r2, #LENGTH_UBOOT

bl nand_read_ll

tst r0, #0x0

beq ok_nand_read

bad_nand_read:

loop2:

b loop2@ infinite loop

ok_nand_read:

@ verify

mov r0, #0

ldr r1, =TEXT_BASE

mov r2, #0x400@ 4 bytes * 1024 = 4K-bytes

go_next:

ldr r3, [r0], #4

ldr r4, [r1], #4

teq r3, r4

bne notmatch

subs r2, r2, #4

beq stack_setup

bne go_next

notmatch:

loop3:

b loop3@ infinite loop

#endif

#ifdef CONFIG_S3C2410

/* Offset */

#define oNFCONF 0x00

#define oNFCMD 0x04

#define oNFSTAT 0x10

@ reset NAND

mov r1, #NAND_CTL_BASE

ldr r2, =0xf830@ initial value

str r2, [r1, #oNFCONF]

ldr r2, [r1, #oNFCONF]

bic r2, r2, #0x800@ enable chip

str r2, [r1, #oNFCONF]

mov r2, #0xff@ RESET command

strb r2, [r1, #oNFCMD]

mov r3, #0@ wait

nand1:

add r3, r3, #0x1

cmp r3, #0xa

blt nand1

nand2:

ldr r2, [r1, #oNFSTAT]@ wait ready

tst r2, #0x1

beq nand2

ldr r2, [r1, #oNFCONF]

orr r2, r2, #0x800@ disable chip

str r2, [r1, #oNFCONF]

@ get read to call C functions (for nand_read())

ldr sp, DW_STACK_START@ setup stack pointer

mov fp, #0@ no previous frame, so fp=0

@ copy U-Boot to RAM

ldr r0, =TEXT_BASE

mov r1, #0x0

mov r2, #LENGTH_UBOOT

bl nand_read_ll

tst r0, #0x0

beq ok_nand_read

bad_nand_read:

loop2:

b loop2@ infinite loop

ok_nand_read:

@ verify

mov r0, #0

ldr r1, =TEXT_BASE

mov r2, #0x400@ 4 bytes * 1024 = 4K-bytes

go_next:

ldr r3, [r0], #4

ldr r4, [r1], #4

teq r3, r4

bne notmatch

subs r2, r2, #4

beq stack_setup

bne go_next

notmatch:

loop3:

b loop3@ infinite loop

#endif

/***************** NAND_BOOT *************************************************/

/***************** NOR_BOOT *************************************************/

relocate: /* relocate U-Boot to RAM */

/*********** CHECK_FOR_MAGIC_NUMBER***************/

ldr r1, =(0xdeadbeef)

cmp r0, r1

bne loop3

/*********** CHECK_FOR_MAGIC_NUMBER***************/

adr r0, _start/* r0 <- current position of code */

ldr r1, _TEXT_BASE/* test if we run from flash or RAM */

ldr r2, _armboot_start

ldr r3, _bss_start

sub r2, r3, r2/* r2 <- size of armboot */

add r2, r0, r2/* r2 <- source end address */

copy_loop:

ldmia r0!, {r3-r10}/* copy from source address [r0] */

stmia r1!, {r3-r10}/* copy to target address [r1] */

cmp r0, r2/* until source end addreee [r2] */

ble copy_loop

/***************** NOR_BOOT *************************************************/

/*иӢҘд»Јз ҒеңЁramдёӯиҝҗиЎҢпјҢеҲҷзӣҙжҺҘи·іеҲ°жӯӨеӨ„пјҢејҖе§Ӣи®ҫзҪ®sp*/

/* Set up the stack */

stack_setup:

ldr r0, _TEXT_BASE/* upper 128 KiB: relocated uboot */

sub r0, r0, #CONFIG_SYS_MALLOC_LEN/* malloc area */

sub r0, r0, #CONFIG_SYS_GBL_DATA_SIZE /* bdinfo */

#ifdef CONFIG_USE_IRQ

sub r0, r0, #(CONFIG_STACKSIZE_IRQ+CONFIG_STACKSIZE_FIQ)

#endif

subsp, r0, #12

/* leave 3 words for abort-stack */

/*еҜ№з…§дёӢеӣҫйҳ…иҜ»дёҠиҝ°д»Јз ҒпјҢз”ЁжҲ·ж ҲеҢәspеҫҖдёӢз”ҹй•ҝ*/

/*жё…йӣ¶bss*/

clear_bss:

ldr r0, _bss_start/* find start of bss segment */

ldr r1, _bss_end/* stop here */

mov r2, #0x00000000/* clear */

/*жё…йӣ¶еҫӘзҺҜпјҢз©әй—ҙдёә32дҪҚпјҢжүҖд»Ҙadd r0,r0,#4(4дёӘеӯ—иҠӮ)*/

clbss_l:str r2, [r0]/* clear loop... */

add r0, r0, #4

cmp r0, r1

ble clbss_l

/*еҮҶеӨҮи·іиҪ¬еҲ°stage2пјҢldrдёҺbзҡ„еҢәеҲ«пјҹ

*start_armbootеңЁlib_arm/board.cж–Ү件дёӯ

*/

ldrpc, _start_armboot

#if defined(CONFIG_MINI2440_LED)

#define GPIO_CTL_BASE 0x56000000

#define oGPIO_B 0x10

#define oGPIO_CON 0x0

/* R/W, Configures the pins of the port */

#define oGPIO_DAT 0x4

#define oGPIO_UP 0x8

/* R/W, Pull-up disable register */

mov r1, #GPIO_CTL_BASE

add r1, r1, #oGPIO_B

ldr r2, =0x295551

str r2, [r1, #oGPIO_CON]

mov r2, #0xff

str r2, [r1, #oGPIO_UP]

ldr r2, =0x1c1

str r2, [r1, #oGPIO_DAT]

#endif

_start_armboot: .word start_armboot

#define STACK_BASE 0x33f00000

#define STACK_SIZE 0x10000

.align

2

DW_STACK_START: .wordSTACK_BASE+STACK_SIZE-4

/*

*************************************************************************

*

* CPU_init_critical registers

*

* setup important registers

* setup memory timing

*

*

*/

#ifndef CONFIG_SKIP_LOWLEVEL_INIT

cpu_init_crit:

/*

* flush v4 I/D caches

*жё…йӣ¶ж•°жҚ®cacheдёҺжҢҮд»Өcache

*жё…йӣ¶TLB

*/

mov r0, #0

mcr p15, 0, r0, c7, c7, 0/* flush v3/v4 cache */

mcr p15, 0, r0, c8, c7, 0/* flush v4 TLB */

/*

* disable MMU stuff and caches

*е…ій—ӯMMUдёҺcacheпјҢеҝ…йЎ»е…ій—ӯпјҢдёҚдјҡеӣһжңүи„Ҹж•°жҚ®пјҢеҪұе“ҚжӯЈзЎ®иҝҗиЎҢ

*/

mrc p15, 0, r0, c1, c0, 0

bic r0, r0, #0x00002300@ clear bits 13, 9:8 (--V- --RS)

bic r0, r0, #0x00000087@ clear bits 7, 2:0 (B--- -CAM)

orr r0, r0, #0x00000002@ set bit 2 (A) Align

orr r0, r0, #0x00001000@ set bit 12 (I) I-Cache

mcr p15, 0, r0, c1, c0, 0

/*

* before relocating, we have to setup RAM timing

* because memory timing is board-dependend, you will

* find a lowlevel_init.S in your board directory.

*/

mov ip, lr

/*еңЁcpu_init_critдёӯеҸҲи°ғз”ЁеӨ–йғЁеҮҪж•°lowlevel_initпјҢеӣ жӯӨиҰҒдәӢе…ҲдҝқжҠӨеҘҪlrеҜ„еӯҳеҷЁзҡ„еҶ…е®№пјҢеҪ“иҝ”еӣһж—¶еҖҷпјҢеҶҚжҒўеӨҚе®ғ

*еҜ„еӯҳеҷЁr12пјҢз”ЁдҪңиҝҮзЁӢи°ғз”Ёдёӯй—ҙдёҙж—¶еҜ„еӯҳеҷЁпјҢи®°дҪңipпјҢеңЁеӯҗзЁӢеәҸй—ҙзҡ„иҝһжҺҘд»Јз Ғж®өдёӯеёёжңүиҝҷз§ҚдҪҝ用规еҲҷ

*еҜ„еӯҳеҷЁr14пјҢз§°дёәиҝһжҺҘеҜ„еӯҳеҷЁпјҢи®°дҪңlrпјҢе®ғз”ЁдәҺдҝқеӯҳеӯҗзЁӢеәҸзҡ„иҝ”еӣһең°еқҖ

*/

bl lowlevel_init;дҫқиө–е…·дҪ“зҡ„board

mov lr, ip

mov pc, lr;дҝқеӯҳcpu_init_critзҡ„иҝ”еӣһең°еқҖ

#endif /* CONFIG_SKIP_LOWLEVEL_INIT */

/*

*************************************************************************

*

* Interrupt handling

*

*************************************************************************

*/

@

@ IRQ stack frame.

@

#define S_FRAME_SIZE 72

#define S_OLD_R0 68

#define S_PSR 64

#define S_PC 60

#define S_LR 56

#define S_SP 52

#define S_IP 48

#define S_FP 44

#define S_R10 40

#define S_R9 36

#define S_R8 32

#define S_R7 28

#define S_R6 24

#define S_R5 20

#define S_R4 16

#define S_R3 12

#define S_R2 8

#define S_R1 4

#define S_R0 0

#define MODE_SVC 0x13

#define I_BIT 0x80

/*

* use bad_save_user_regs for abort/prefetch/undef/swi ...

* use irq_save_user_regs / irq_restore_user_regs for IRQ/FIQ handling

*/

.macro

bad_save_user_regs

sub sp, sp, #S_FRAME_SIZE

stmia sp, {r0 - r12}@ Calling r0-r12

ldr r2, _armboot_start

sub r2, r2, #(CONFIG_STACKSIZE)

sub r2, r2, #(CONFIG_SYS_MALLOC_LEN)

/* set base 2 words into abort stack */

sub r2, r2, #(CONFIG_SYS_GBL_DATA_SIZE+8)

ldmia r2, {r2 - r3}@ get pc, cpsr

add r0, sp, #S_FRAME_SIZE@ restore sp_SVC

add r5, sp, #S_SP

mov r1, lr

stmia r5, {r0 - r3}@ save sp_SVC, lr_SVC, pc, cpsr

mov r0, sp

.endm

.macro

irq_save_user_regs

sub sp, sp, #S_FRAME_SIZE

stmia sp, {r0 - r12}@ Calling r0-r12

add r7, sp, #S_PC

stmdb r7, {sp, lr}^@ Calling SP, LR

str lr, [r7, #0]@ Save calling PC

mrs r6, spsr

str r6, [r7, #4]@ Save CPSR

str r0, [r7, #8]@ Save OLD_R0

mov r0, sp

.endm

.macro

irq_restore_user_regs

ldmia sp, {r0 - lr}^@ Calling r0 - lr

mov r0, r0

ldr lr, [sp, #S_PC]@ Get PC

add sp, sp, #S_FRAME_SIZE

/* return & move spsr_svc into cpsr */

subs pc, lr, #4

.endm

.macro get_bad_stack

ldr r13, _armboot_start@ setup our mode stack

sub r13, r13, #(CONFIG_STACKSIZE)

sub r13, r13, #(CONFIG_SYS_MALLOC_LEN)

/* reserve a couple spots in abort stack */

sub r13, r13, #(CONFIG_SYS_GBL_DATA_SIZE+8)

str lr, [r13]@ save caller lr / spsr

mrs lr, spsr

str lr, [r13, #4]

mov r13, #MODE_SVC@ prepare SVC-Mode

@ msr spsr_c, r13

msr spsr, r13

mov lr, pc

movs pc, lr

.endm

.macro get_irq_stack@ setup IRQ stack

ldr sp, IRQ_STACK_START

.endm

.macro get_fiq_stack@ setup FIQ stack

ldr sp, FIQ_STACK_START

.endm

/*

* exception handlers

*/

.align 5

undefined_instruction:

get_bad_stack

bad_save_user_regs

bl do_undefined_instruction

.align

5

software_interrupt:

get_bad_stack

bad_save_user_regs

bl do_software_interrupt

.align

5

prefetch_abort:

get_bad_stack

bad_save_user_regs

bl do_prefetch_abort

.align

5

data_abort:

get_bad_stack

bad_save_user_regs

bl do_data_abort

.align

5

not_used:

get_bad_stack

bad_save_user_regs

bl do_not_used

#ifdef CONFIG_USE_IRQ

.align

5

irq:

//Apollo +

/*

get_irq_stack

irq_save_user_regs

bl do_irq

irq_restore_user_regs

*/

/* use IRQ for USB and DMA */

sub lr, lr, #4 @ the return address

ldr sp, IRQ_STACK_START @ the stack for irq

stmdb sp!, { r0-r12,lr } @ save registers

ldr lr, =int_return @ set the return addr

ldr pc, =IRQ_Handle @ call the isr

int_return:

ldmia sp!, { r0-r12,pc }^ @ return from interrupt

//Apollo -

.align

5

fiq:

get_fiq_stack

/* someone ought to write a more effiction fiq_save_user_regs */

irq_save_user_regs

bl do_fiq

irq_restore_user_regs

#else

.align

5

irq:

get_bad_stack

bad_save_user_regs

bl do_irq

.align

5

fiq:

get_bad_stack

bad_save_user_regs

bl do_fiq

#endif

- 2011-11-10 14:48

- жөҸи§Ҳ 1174

- иҜ„и®ә(0)

- жҹҘзңӢжӣҙеӨҡ

зӣёе…іжҺЁиҚҗ

жң¬ж–Үд»Һд»ҘдёӢеҮ дёӘж–№йқўзІ—жө…ең°еҲҶжһҗu-boot并移жӨҚеҲ°FS2410жқҝдёҠпјҡ 1гҖҒu-bootе·ҘзЁӢзҡ„жҖ»дҪ“з»“жһ„ 2гҖҒu-bootзҡ„жөҒзЁӢгҖҒдё»иҰҒзҡ„ж•°жҚ®з»“жһ„гҖҒеҶ…еӯҳеҲҶй…ҚгҖӮ 3гҖҒu-bootзҡ„йҮҚиҰҒз»ҶиҠӮпјҢдё»иҰҒеҲҶжһҗжөҒзЁӢдёӯеҗ„еҮҪж•°зҡ„еҠҹиғҪгҖӮ 4гҖҒеҹәдәҺFS2410жқҝеӯҗзҡ„u-boot...

U-Boot жәҗз ҒеҲҶжһҗпјҲu-boot-2009.03пјүпјҢеҗҺз»ӯдјҡжңү移жӨҚиҜҰз»Ҷж•ҷзЁӢгҖӮ

U-Boot-1.3.1жәҗз ҒеҲҶжһҗиҜҫ件пјҢе…Ҙй—ЁU-BootеҲ©еҷЁ

ејҖеҸ‘жқҝдёҠз”өеҗҺпјҢжү§иЎҢU-Bootзҡ„第дёҖжқЎжҢҮд»ӨпјҢ然еҗҺйЎәеәҸжү§иЎҢU-BootеҗҜеҠЁеҮҪж•°гҖӮеҮҪж•°и°ғз”ЁйЎәеәҸеҰӮеӣҫ6.3жүҖзӨәгҖӮ зңӢдёҖдёӢboard/smsk2410/u-boot.ldsиҝҷдёӘй“ҫжҺҘи„ҡжң¬пјҢеҸҜд»ҘзҹҘйҒ“зӣ®ж ҮзЁӢеәҸзҡ„еҗ„йғЁеҲҶй“ҫжҺҘйЎәеәҸгҖӮ第дёҖдёӘиҰҒй“ҫжҺҘзҡ„жҳҜcpu/arm920t/...

жң¬ж–ҮеҲҶжһҗдәҶu-boot-2018.09пјҢеҜ№дәҺеӯҰд№ е’Ң移жӨҚu-bootзҡ„жңӢеҸӢдјҡжңүеё®еҠ©

u-bootзҡ„MakefileеҲҶжһҗ u-bootзҡ„MakefileеҲҶжһҗ

иҜҘж–Ү件жҳҜu-bootеҲҶжһҗ第дёҖйҳ¶ж®өе’Ң第дәҢйҳ¶ж®өжөҒзЁӢеӣҫпјҡlowlevel_initе’Ңstart_armbootпјҢе…·дҪ“еҲҶжһҗзҡ„ж–Үз« еҰӮдёӢпјҡ lowlevel_initпјҡhttps://blog.csdn.net/zi_yang_/article/details/89182278 start_armbootпјҡ...

U-BootеҗҜеҠЁиҝҮзЁӢе®Ңе…ЁеҲҶжһҗ,U-BootеҗҜеҠЁеҶ…ж ёзҡ„иҝҮзЁӢеҸҜд»ҘеҲҶдёәдёӨдёӘйҳ¶ж®ө

еҫҲеҘҪзҡ„U-bootжәҗз ҒеҲҶжһҗиө„ж–ҷпјҢйқһеёёиҜҰз»ҶпјҢеҸ—зӣҠеҢӘжө…

u-boot-2010.06жәҗз Ғmakeжү§иЎҢиҝҮзЁӢ

U-BOOT MAKEFILE еҲҶжһҗ

иҜҰз»Ҷзҡ„и®Іи§ЈдәҶu-bootеҗҜеҠЁд»Јз Ғзҡ„移жӨҚиҝҮзЁӢпјҢиҝҳжңүеёёйҒҮеҲ°зҡ„й—®йўҳеҲҶжһҗи§ЈеҶіпјҢu-boot иҝҗиЎҢиҪЁиҝ№зҡ„иҜҰз»ҶеҲҶжһҗпјҢиғҪи®©дҪ дёҚд»…д»…еӯҰдјҡ移жӨҚu-bootпјҢиҝҳиғҪзҹҘйҒ“移жӨҚu-bootзҡ„з»ҶиҠӮеҺҹзҗҶгҖӮ

U-bootеңЁARM9дёӢйқўзҡ„移жӨҚдёҺеҲҶжһҗпјҢиҜҰз»Ҷд»Ӣз»ҚU-Bootд»Јз Ғз»„жҲҗ

U-BOOTжәҗз ҒеҲҶжһҗеҸҠ移жӨҚ жң¬ж–Үд»Һд»ҘдёӢеҮ дёӘж–№йқўзІ—жө…ең°еҲҶжһҗu-boot并移жӨҚеҲ°FS2410жқҝдёҠпјҡ 1гҖҒu-bootе·ҘзЁӢзҡ„жҖ»дҪ“з»“жһ„ 2гҖҒu-bootзҡ„жөҒзЁӢгҖҒдё»иҰҒзҡ„ж•°жҚ®з»“жһ„гҖҒеҶ…еӯҳеҲҶй…ҚгҖӮ 3гҖҒu-bootзҡ„йҮҚиҰҒз»ҶиҠӮпјҢдё»иҰҒеҲҶжһҗжөҒзЁӢдёӯеҗ„еҮҪж•°зҡ„еҠҹиғҪгҖӮ 4гҖҒ...

u-boot makefile еҲҶжһҗ

иҝҷжҳҜеҚҡеҲӣ科жҠҖзҡ„йҖҡз”Ёbootloader u-bootзҡ„и®Іи§ЈиҜҫ件пјҢеҢ…жӢ¬йғЁеҲҶд»Јз Ғе’Ңеј•еҜјиҝҮзЁӢеҲҶжһҗгҖӮ

u-bootеҲҶжһҗ,ubootд»Јз ҒиҜҰз»ҶеҲҶжһҗ,иҝҷжҳҜдёҖжң¬иө„ж·ұдәәеЈ«еҶҷзҡ„ubootеҲҶжһҗд»Јз ҒпјҢдёӘдәәзңӢдәҶд»ҘеҗҺж„ҹи§үеҸ—зӣҠеҢӘжө…

u-boot2017.01еҗҜеҠЁиҝҮзЁӢеҲҶжһҗпјҢд»Ҙpptзҡ„ж–№ејҸеҜ№uboot2017.11зҡ„еҗҜеҠЁиҝҮзЁӢиҝӣиЎҢеҲҶжһҗпјҢдё»иҰҒеҲҶжһҗдәҶеҗҜеҠЁиҝҮзЁӢеҮҪж•°зҡ„и°ғз”ЁиҝҮзЁӢ